| ADMISSION NUMBER |  |  |  |  |  |  |  |  |  |  |  |

|------------------|--|--|--|--|--|--|--|--|--|--|--|

|                  |  |  |  |  |  |  |  |  |  |  |  |

## **School of Basic Sciences**

Bachelor of Science Honours in Mathematics Semester End Examination - May 2024

Duration : 180 Minutes Max Marks : 100

## Sem VI - C1UD604B - Analog and Digital Principles and Applications

<u>General Instructions</u> Answer to the specific question asked Draw neat, labelled diagrams wherever necessary Approved data hand books are allowed subject to verification by the Invigilator

- 1) Design the Ex-OR gate using NAND gates. K1 (3)

- <sup>2)</sup> Write the expression for function Y in SOP & POS forms. K2 (4)  $\frac{B C Y}{0 0 0}$

- 011

- 100

- 111

- Explain the nature of Fermi-Dirac distribution function and interpret it K<sup>2</sup> (6) graphically at different temperatures.

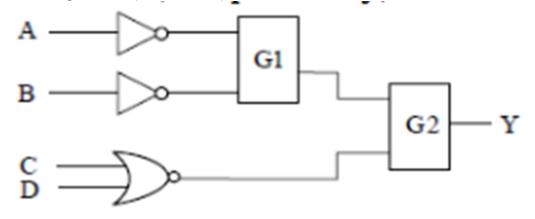

- <sup>4)</sup> Indentify the name of logic gates at G1 and G2 in the given circuit  $K^{3}$  (6) considering the output Y is required to be  $Y = AB + \overline{CD}$

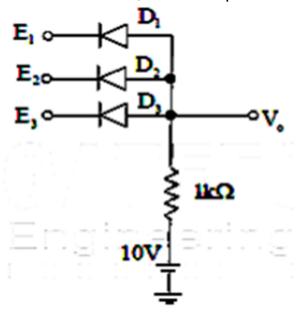

5) Write the name of logic gate of given circuit shown, diodes  $K^{3}(6)$   $D_{1}, D_{2}, and D_{3}$  are ideal, and the inputs  $E_{1}, E_{2}$  and  $E_{3}$

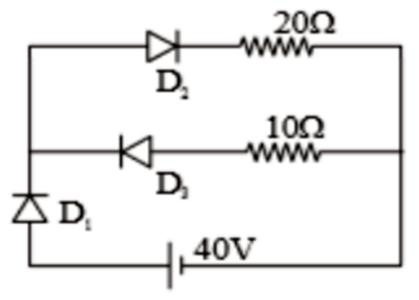

6) Three ideal diodes are connected to the battery as shown in the circuit. Find the current supplied by the battery (see Fig.). If the polarity of the battery is reversed, then calculate the current in same circuit.

- <sup>7)</sup> Simply the following Boolean functions using K –Map F(A,B,C,D.E) =  $\Sigma$  (0,2,4,6,9,11,13,15,17,21,25,27,29,31)

- 8) Write the truth table of full adder and draw the full adder diagram K4 (8) using NAND gates?

- 9) Explain with logic diagram of 4-bit serial-in, parallel-out, shift register K4 (12)

- 10) Design a Full Adder using two Half Adder and OR gate, draw the Block diagram with logic circuit ?

- <sup>11)</sup> Find the resistance of an intrinsic Ge rod 1 mm long, 1 mm wide and 1  $K^{5}$  (15) mm thick at 300 K. the intrinsic carrier density 2.5  $X \ 10^{19} m^{-3}$  is at 300 K and the mobility of electron and hole are 0.39 and 0.19  $m^2 v^{-1} s^{-1}$ .

## OR

Germanium has a donor type of impurity added to the extent of one to the atom per 108 germanium atoms. What effect does this have on the conductivity of the material at 27°C? Given:  $\mu_e = 0.39m^2V^{-1}s^{-1}and \mu_p = 0.19m^2V^{-1}s^{-1}$  of intrinsic germanium. Electron mobility of the doped germanium is  $0.38 m^2V^{-1}s^{-1}$ . Given:  $K_B = 1.38 X \ 10^{-23}J/k, h = 6.626x 10^{-34}J - s \ and \ m_0 = 9.1 X \ 10^{-31}kg.$

<sup>12)</sup> Design SR flip-flop using JK flip-flop.

K6 (12)

## OR

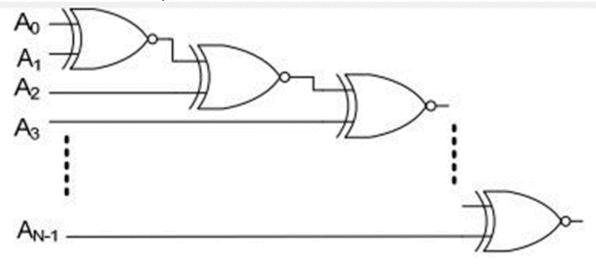

N number of Ex-NOR gates are connected as show in figure. How <sup>K6 (12)</sup> does this circuit work? Explain?