**Course Code: BSCP3005**

**Course Name: Digital System and Application**

# Serial In and Parallel Out (SIPO) Register

#### **Contents:**

- 1. Introduction

- 2. Block Diagram of SIPO

- 3. Working

Course Code: BSCP3005 Course Name: Digital System and Application

**Introduction: Serial Input Parallel Output register**

- In such types of operations, the data is entered serially and taken out in parallel fashion.

- Data is loaded bit by bit. The outputs are disabled as long as the data is loading.

- As soon as the data loading gets completed, all the flip-flops contain their required data, the outputs are enabled so that all the loaded data is made available over all the output lines at the same time.

- 4 clock cycles are required to load a four bit word. Hence the speed of operation of SIPO mode is same as that of SISO mode.

**Course Code: BSCP3005**

**Course Name: Digital System and Application**

**Serial Input Parallel Output register**

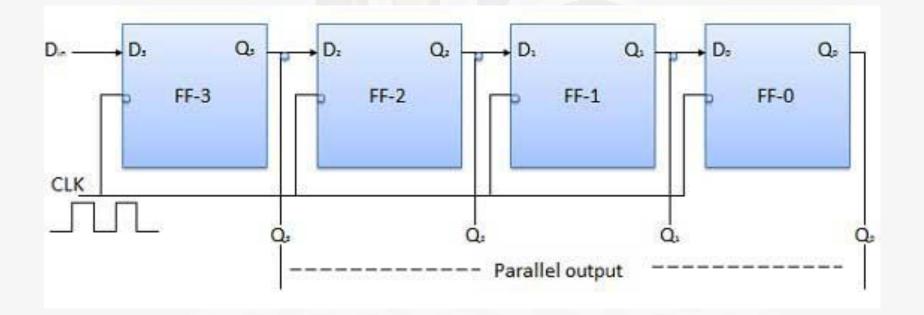

#### **Block Diagram**

Course Code: BSCP3005

**Course Name: Digital System and Application**

#### Serial Input Parallel Output register- Explanation

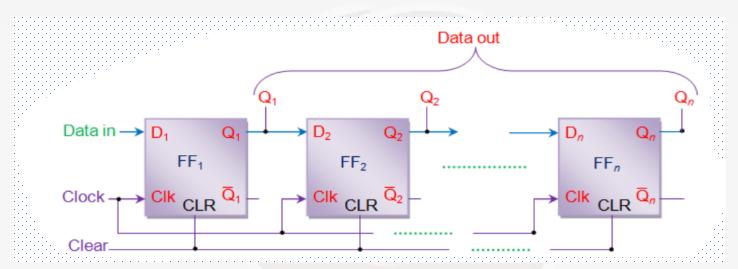

In **Serial In Parallel Out (SIPO) shift registers**, the data is stored into the register serially while it is retrieved from it in parallel-fashion. Figure shows an n-bit synchronous **SIPO shift register** sensitive to positive edge of the clock pulse. Here the data word which is to be stored (Data in) is fed serially at the input of the first flip-flop ( $D_1$  of  $FF_1$ ). It is also seen that the inputs of all other flip-flops (except the first flip-flop  $FF_1$ ) are driven by the outputs of the preceding ones say for example, the input of  $FF_2$  is driven by the output of  $FF_1$ . In this kind of shift register, the data stored within the register is obtained as a parallel-output data word (Data out) at the individual output pins of the flip-flops ( $Q_1$  to  $Q_n$ ).

Course Code: BSCP3005

**Course Name: Digital System and Application**

#### **Serial Input Parallel Output register**

In general, the register contents are cleared by applying high on the clear pins of all the flip-flops at the initial stage. After this, the first bit,  $B_1$  of the input data word is fed at the  $D_1$  pin of FF

This bit  $(B_1)$  will enter into  $FF_1$ , get stored and thereby appears at its output  $Q_1$  on the appearance of first leading edge of the clock. Further at the second clock tick, the bit  $B_1$  right-shifts and gets stored into  $FF_2$  while appearing at its output pin  $Q_2$  while a new bit,  $B_2$  enters into  $FF_1$ . Similarly at each clock tick the data within the register moves towards right by a single bit while a new bit of the input word enters into the register. Meanwhile one can extract the bits stored within the register in parallel-fashion at the individual flip-flop outputs.

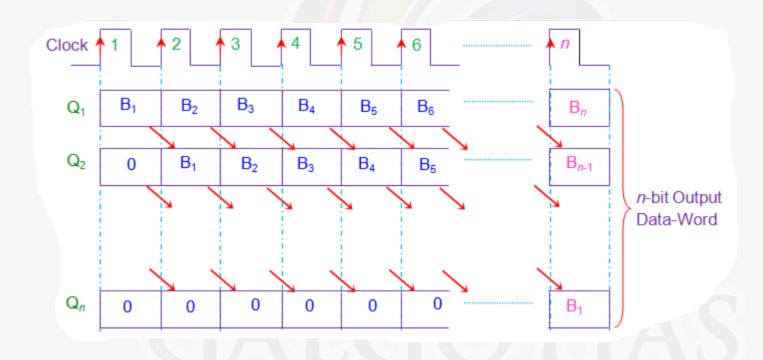

Analyzing on the same grounds, one can note that the n-bit input data word is obtained as an n-bit output data word from the shift register at the rising edge of the n<sup>th</sup> clock pulse. This working of the shift-register can be summarized as in Table I and the corresponding wave forms are given by Figure.

Course Code: BSCP3005

**Course Name: Digital System and Application**

#### **Serial Input Parallel Output register**

Table I Data Movement in Right-Shift SIPO Shift Register

| Clock Cycle | Data in          | $Q_1$              | $Q_2$                           |     | Q <sub>n</sub>       |

|-------------|------------------|--------------------|---------------------------------|-----|----------------------|

| 1           | B <sub>1</sub> — | → B <sub>1</sub>   | 0                               |     | 0                    |

| 2           | B <sub>2</sub> — | → B <sub>2</sub> 、 | <sup>™</sup> B <sub>1</sub> 、   |     | <b>7</b> 0           |

| 3           | B <sub>3</sub> — | → B <sub>3</sub> 、 | $^{\mathbf{A}}$ $B_2$ ,         | ··· | 20                   |

| 4           | B <sub>4</sub> — | → B <sub>4</sub>   | <sup>™</sup> B <sub>3</sub> 、   | ··· | 20                   |

| 5           | B <sub>5</sub> — | → B <sub>5</sub> 、 | <sup>▶</sup> B <sub>4</sub> 、   |     | / <sub>2</sub> 0     |

| 6           | B <sub>6</sub>   | → B <sub>6</sub> 、 | <sup>™</sup> B <sub>5</sub> 、   |     | 7 0                  |

|             |                  |                    |                                 | 7   | × .                  |

| -           |                  | -                  |                                 |     | .                    |

| -           |                  |                    |                                 |     |                      |

| n           | $B_n$ —          | $\rightarrow B_n$  | $^{\mathbf{A}}\mathbf{B}_{n-1}$ |     | $^{\mathbf{A}}B_{1}$ |

Output of SIPO (right-shift) Shift Register

In the right-shift SIPO shift-register, data bits shift from left to right for each clock tick.

**Course Code: BSCP3005**

**Course Name: Digital System and Application**

#### **Serial Input Parallel Output register**

Output Waveform of *n*-bit Right-Shift SIPO Shift Register

Course Code: BSCP3005 Course Name: Digital System and Application

#### **References:**

- Digital Principles and Applications, A.P. Malvino, D. P. Leach and Saha, 7<sup>th</sup> Ed., 2011, Tata McGraw Hill

- Digital Fundamentals, Thomas L. Floyd, 11th Ed., 2015, Pearson Education Limited

- Modern Digital Electronics, R P Jain, 4th Ed., 2010, Tata McGraw Hill

Name of the Faculty: Dr. Prabhakar Singh

**Program Name: B.Sc.(H) Physics**