**Course Code: BSCP3005**

**Course Name: Digital System and Application**

**Universal Logic Gates**

#### **Contents:**

- NAND Gate

- NAND Gate as Universal logic gate

- NOR Gate

- NOR Gate as Universal logic gate

Name of the Faculty: Dr. Prabhakar Singh

**Course Code: BSCP3005**

**Course Name: Digital System and Application**

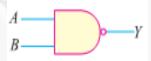

#### NAND (NOT+AND) Gate

It is a combination of AND gate and NOT gate. In other words, output of

AND gate is connected to the input of a NOT gate as shown in Fig.. Clearly, the output

of a NAND gate is opposite to the AND gate. This is illustrated in the truth table for the NAND gate. Note that truth table for NAND gate is developed by inverting the outputs of the AND gate. This Boolean expression can be read as Y = not A . B. To perform the Boolean algebra operation first the inputs must be ANDed and then the inversion is performed. Note that output from a NAND

gate is always 1 except when all of the inputs are 1.

The little bubble (small circle) on the right end of the symbol means to invert the AND.

The Boolean expression for NAND function is  $Y = \overline{A \cdot B}$ Inputs  $A = A \cdot B$ Output  $Y = \overline{A \cdot B}$

| Inputs |   | Output  |         |

|--------|---|---------|---------|

| A      | В | AND(Y') | NAND(Y) |

| 0      | 0 | 0       | 1       |

| 1      | 0 | 0       | 1       |

| 0      | 1 | 0       | 1       |

| 1      | 1 | 1       | 0       |

Name of the Faculty: Dr. Prabhakar Singh

**Course Code: BSCP3005**

**Course Name: Digital System and Application**

#### NAND Gate as a Universal Gate

The NAND gate is universal gate because its repeated use can produce other logic gates.

The table shows how NAND gates can be connected to produce inverter (i.e., NOT gate), AND gate and OR gate.

| Logic<br>Function | Symbol                                 | Circuit using NAND gates only    |

|-------------------|----------------------------------------|----------------------------------|

| Inverter          | A————————————————————————————————————— | $A \longrightarrow \overline{A}$ |

| AND               | A.B                                    | A Y' Y                           |

| OR                | $A \longrightarrow A + B$              | A Y' B Y"                        |

**Course Code: BSCP3005**

**Course Name: Digital System and Application**

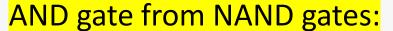

#### NOT gate from NAND gate:

When two inputs of NAND gate are joined together so that it has one input, the resulting circuit is NOT gate. The truth table also shows this fact.

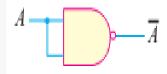

For this purpose, we use two NAND gates in a manner as shown above. The output of first NAND gate is given to the second NAND gate acting as inverter (i.e., inputs of NAND gate joined). The resulting circuit is the AND gate. The output Y' of first NAND gate (AND gate followed by NOT gate) is inverted output of AND gate. The second NAND gate acting as

inverter further inverts it so that the final output Y is

that of AND gate. The truth table also shows this fact.

| A | B (= A) | Y |

|---|---------|---|

| 0 | 0       | 1 |

| 1 | I.      | 0 |

| A | В | Y | Y |

|---|---|---|---|

| 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Name of the Faculty: Dr. Prabhakar Singh

**Course Code: BSCP3005**

**Course Name: Digital System and Application**

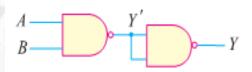

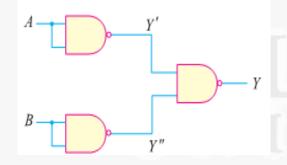

#### OR gate from NAND gates:

For this purpose, we use three NAND gates in a manner as shown above. The first two NAND gates are operated as NOT gates and their outputs are fed to the third. The resulting circuit is OR gate. This fact is also indicated by the truth table

| A | В | $Y' = \overline{A}$ | $Y'' = \overline{B}$ | Y |

|---|---|---------------------|----------------------|---|

| 0 | 0 | 1                   | 1                    | 0 |

| 1 | 0 | 0                   | 1                    | 1 |

| 0 | 1 | 1                   | 0                    | 1 |

| 1 | 1 | 0                   | 0                    | 1 |

**Course Code: BSCP3005**

**Course Name: Digital System and Application**

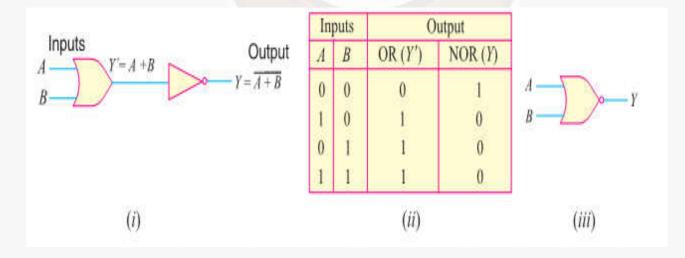

#### NOR Gate (NOT+OR gate)

It is a combination of OR gate and NOT gate. In other words, output of OR gate is connected to the input of a NOT gate as shown in Fig. Note that output of OR gate is inverted to form NOR gate. This is illustrated in the truth table for NOR gate. It is clear that truth table for NOR gate is developed by inverting the outputs of the OR gate.

Name of the Faculty: Dr. Prabhakar Singh

**Course Code: BSCP3005**

**Course Name: Digital System and Application**

# NOR Gate (NOT+OR gate)

The Boolean expression for NOR function is:

$$Y = \overline{A + B}$$

This Boolean expression can be read as Y = not A or B. To perform the Boolean algebra operation, first the inputs must be ORed and then the inversion is performed. Note that output from a NOR

gate is high (1) only when all the inputs are low (0). If any of the inputs is high (1), the output is low

(0). Fig. iii shows the logic symbol for a NOR gate. The bubble (small circle) at the Y output indicates inversion.

**Course Code: BSCP3005**

**Course Name: Digital System and Application**

#### NOR Gate as a Universal Gate

NOR gates are so-called "universal gates" that can be combined to form any other kind of logic gate.

#### NOR Gate as Inverter:

The figure shows in which a NOR gate can be used as an inverter (NOT gate).

**OR Gate using NOR Gates:**

AND Gate Using only NOR Gates

Name of the Faculty: Dr. Prabhakar Singh

Course Code: BSCP3005 Course Name: Digital System and Application

#### **References:**

- Digital Principles and Applications, A.P. Malvino, D. P. Leach and Saha, 7<sup>th</sup> Ed., 2011, Tata McGraw Hill

- Digital Fundamentals, Thomas L. Floyd, 11th Ed., 2015, Pearson Education Limited

- Modern Digital Electronics, R P Jain, 4th Ed., 2010, Tata McGraw Hill

GALGOTIAS UNIVERSITY

Name of the Faculty: Dr. Prabhakar Singh